### **CYCLE FABRICATIONS ELECTRONIQUES**

# INTEGRER L'ELECTRONIQUE DE PUISSANCE « MODERNE » DANS LES SYSTEMES

Session organisée par le pôle de compétitité

Les 14, 15 et 16 octobre 2024 STMicroelectronics, Tours

FRAMATECH S.A. au capital de 38112 Euros Etudes & mises en œuvre de stratégies industrielles internationales Hautes Technologies

4 boulevard d'Arras - 13004 Marseille - France Tél. +33 491 95 55 70 / Fax. +33 491 95 55 75 / Mail : contact@framatech.fr Organisme de formation n° 93060115506 – Siret 344 351 879 00046 – NAF 742C – RC88B126 Web : www.framatech.fr

### **CYCLE FABRICATIONS ELECTRONIQUES**

## INTEGRER L'ELECTRONIQUE DE PUISSANCE « MODERNE » DANS LES SYSTEMES

#### NOTE POUR LE LECTEUR QUI N'AURAIT PAS ASSISTE AU SEMINAIRE

La documentation ci-jointe est celle qui a servi de support pour illustrer les exposés faits pendant le séminaire INTEGRER L'ELECTRONIQUE DE PUISSANCE « MODERNE » DANS LES SYSTEMES et ne représente donc qu'une partie des informations données à cette occasion.

FRAMATECH S.A. au capital de 38112 Euros Etudes & mises en œuvre de stratégies industrielles internationales Hautes Technologies

4 boulevard d'Arras - 13004 Marseille - France

Tél. +33 491 95 55 70 / Fax. +33 491 95 55 75 / Mail : contact@framatech.fr

Organisme de formation n° 93060115506 – Siret 344 351 879 00046 – NAF 742C – RC88B126

Web : www.framatech.fr

### **CYCLE FABRICATIONS ELECTRONIQUES**

# INTEGRER L'ELECTRONIQUE DE PUISSANCE « MODERNE » DANS LES SYSTEMES

### **PARTIE IV**

INTEGRATION DE L'ELECTRONIQUE DE PUISSANCE DANS LES SYSTEMES

Roland D'AUTHIER, AXID

FRAMATECH S.A. au capital de 38112 Euros Etudes & mises en œuvre de stratégies industrielles internationales Hautes Technologies

4 boulevard d'Arras - 13004 Marseille - France

Tél. +33 491 95 55 70 / Fax. +33 491 95 55 75 / Mail : contact@framatech.fr

Organisme de formation n° 93060115506 – Siret 344 351 879 00046 – NAF 742C – RC88B126

Web : www.framatech.fr

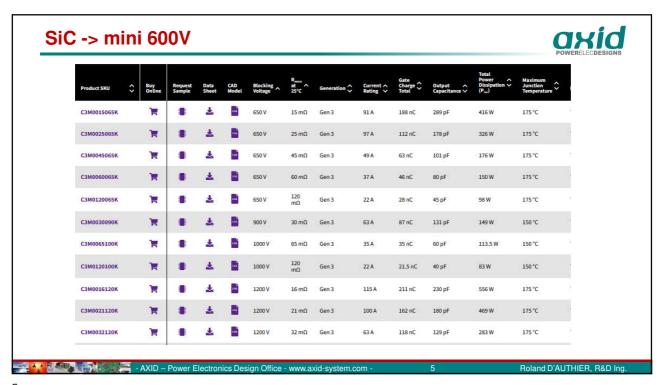

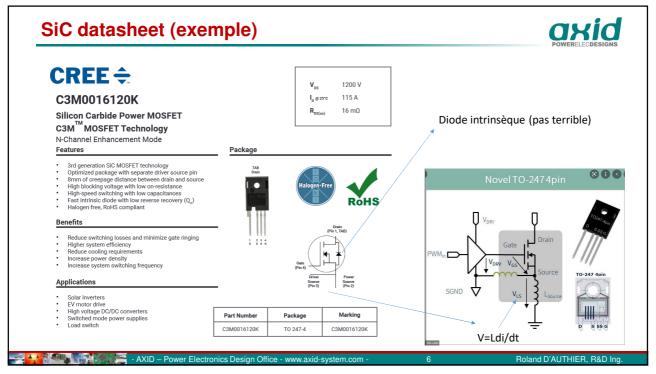

#### SiC datasheet

#### Si on dépasse les max -> on casse

Maximum Ratings ( $T_c = 25$   $^{\circ}$ C unless otherwise specified)

| Symbol                | Parameter                                  | Value          | Unit | Test Conditions                                         | Note    |  |

|-----------------------|--------------------------------------------|----------------|------|---------------------------------------------------------|---------|--|

| V <sub>DSmax</sub>    | Drain - Source Voltage                     | 1200           | ٧    | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 100 μA          |         |  |

| V <sub>GSmax</sub>    | Gate - Source Voltage (dynamic)            | -8/+19         | ٧    | AC (f >1 Hz)                                            | Note 1  |  |

| $V_{GSop}$            | Gate - Source Voltage (static)             | -4/+15         | ٧    | Static                                                  | Note 2  |  |

| Ip                    | Continuous Drain Current                   | 115            | A    | V <sub>GS</sub> = 15 V, T <sub>C</sub> = 25°C           | Fig. 19 |  |

| ID                    | Continuous Drain Current                   |                |      | V <sub>GS</sub> = 15 V, T <sub>C</sub> = 100°C          |         |  |

| I <sub>D(pulse)</sub> | Pulsed Drain Current                       | 250            | Α    | Pulse width t <sub>p</sub> limited by T <sub>jmax</sub> |         |  |

| $P_{D}$               | Power Dissipation                          | 556            | W    | T <sub>C</sub> =25°C, T <sub>J</sub> = 175 °C           | Fig. 20 |  |

| $T_J$ , $T_{atg}$     | Operating Junction and Storage Temperature | -40 to<br>+175 | °C   |                                                         |         |  |

| $T_L$                 | Solder Temperature                         | 260            | °C   | 1.6mm (0.063") from case for 10s                        |         |  |

Note (1): When using MOSFET Body Diode V<sub>GSmax</sub> = -4V/+19V Note (2): MOSFET can also safely operate at 0/+15 V

XID - Power Electronics Design Office - www.axid-system.com -

Roland D'AUTHIER, R&D

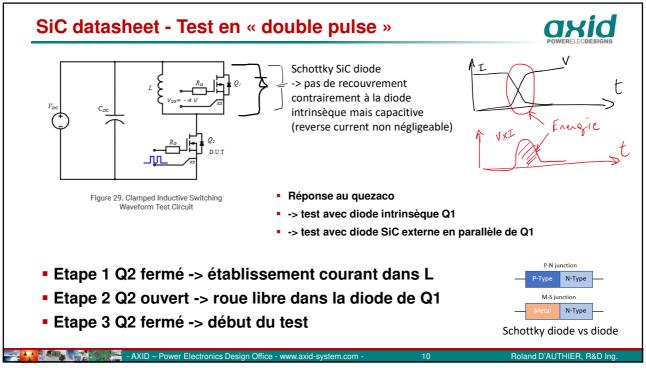

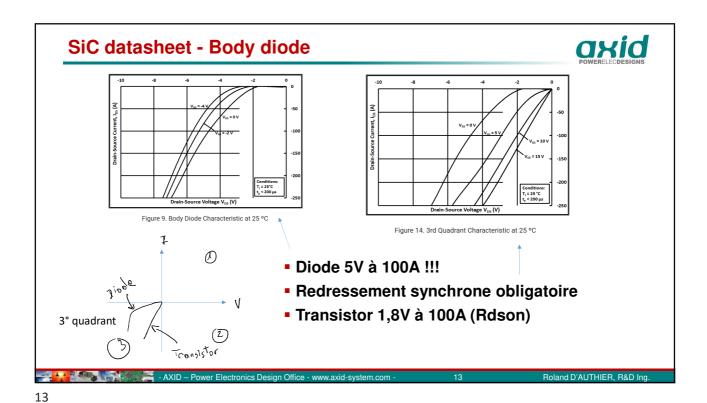

## SiC datasheet -> diode intrinsèque pas si bonne que ça

Reverse Diode Characteristics (T<sub>c</sub> = 25°C unless otherwise specified)

| Symbol                | Parameter                             | Тур. | Max. | Unit | Test Conditions                                                                                                       | Note    |  |

|-----------------------|---------------------------------------|------|------|------|-----------------------------------------------------------------------------------------------------------------------|---------|--|

| $V_{SD}$              | V <sub>SD</sub> Diode Forward Voltage |      |      | ٧    | V <sub>GS</sub> = -4 V, I <sub>SD</sub> = 37.5 A, T <sub>J</sub> = 25 °C                                              | Fig. 8, |  |

| V SD                  | Diode Polward Voltage                 | 4.2  |      | ٧    | V <sub>GS</sub> = -4 V, I <sub>SD</sub> = 37.5 A, T <sub>J</sub> = 175 °C                                             | 9, 10   |  |

| Is                    | Continuous Diode Forward Current      |      | 112  | Α    | V <sub>GS</sub> = -4 V, T <sub>C</sub> = 25°C                                                                         | Note 1  |  |

| I <sub>S, pulse</sub> | Diode pulse Current                   |      | 250  | Α    | $V_{GS}$ = -4 V, pulse width $t_P$ limited by $T_{Jmax}$                                                              | Note 1  |  |

| t <sub>rr</sub>       | Reverse Recover time                  | 30   |      | ns   |                                                                                                                       |         |  |

| $Q_{rr}$              | Reverse Recovery Charge               | 1238 |      | nC   | V <sub>GS</sub> = -4 V, I <sub>SD</sub> = 75 A, V <sub>R</sub> = 800 V<br>dif/dt = 4000 A/µs, T, = 175 °C             | Note 1  |  |

| I <sub>rrm</sub>      | Peak Reverse Recovery Current         | 64   |      | А    |                                                                                                                       |         |  |

| t <sub>rr</sub>       | Reverse Recover time                  | 27   |      | ns   |                                                                                                                       |         |  |

| Q <sub>rr</sub>       | Reverse Recovery Charge               | 1261 |      | nC   | V <sub>GS</sub> = -4 V, I <sub>SD</sub> = 75 A, V <sub>R</sub> = 800 V<br>dif/dt = 5500 A/µs, T <sub>J</sub> = 175 °C | Note 1  |  |

| I <sub>rrm</sub>      | Peak Reverse Recovery Current         | 77   |      | Α    | ]                                                                                                                     |         |  |

9

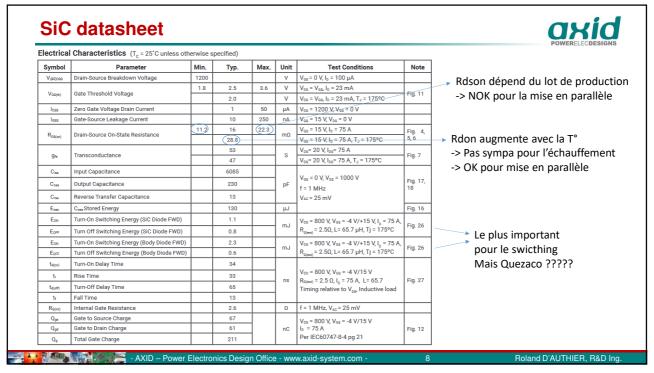

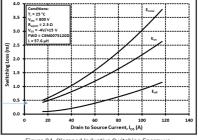

### SiC datasheet - Switching energy

- La fréquence est limitée par l'énergie de switching

- Exemple d'énergie dissipée dans le transistor à 75A/800V

- Environ 3mJ à chaque fermeture + ouverture

- Si switching à  $100kHz -> P=E^*f = 0,003^*100\,000 = 300W$  à dissiper

| Eon              | Turn-On Switching Energy (SiC Diode FWD)   | 1.1 | mJ   | V <sub>DS</sub> = 800 V, V <sub>GS</sub> = -4 V/+15 V, I <sub>D</sub> = 75 A, | Fig. 26  |

|------------------|--------------------------------------------|-----|------|-------------------------------------------------------------------------------|----------|

| E <sub>OFF</sub> | Turn Off Switching Energy (SiC Diode FWD)  | 0.8 | 1110 | $R_{G(ext)} = 2.5\Omega$ , L= 65.7 $\mu$ H, Tj = 175°C                        | 1 ig. 20 |

| Eon              | Turn-On Switching Energy (Body Diode FWD)  | 2.3 |      | V <sub>DS</sub> = 800 V, V <sub>GS</sub> = -4 V/+15 V, I <sub>D</sub> = 75 A, | Fig. 26  |

| Eoff             | Turn Off Switching Energy (Body Diode FWD) | 0.6 | mJ   | R <sub>G(ext)</sub> = 2.5Ω, L= 65.7 μH, Tj = 175°C                            | Fig. 20  |

|                  |                                            |     |      |                                                                               |          |

Rappel : un excellent dissipateur bien ventilé -> environ 0,5°K/W

La jonction ne doit pas dépasser 175°C, Dans « la vraie vie » ont est pas à 75A en permanence

Figure 24. Clamped Inductive Switching Energy vs. Drain Current ( $V_{DD} = 800V$ )

XID – Power Electronics Design Office - www.axid-system.com -

11

Roland D'AUTHIER, R&D Inc

11

### SiC datasheet - Courant de driver

#### • 211nC à chaque ouverture + fermeture

| Q <sub>gs</sub> | Gate to Source Charge | 67  |    | V <sub>DS</sub> = 800 V, V <sub>GS</sub> = -4 V/15 V |         |

|-----------------|-----------------------|-----|----|------------------------------------------------------|---------|

| $Q_{gd}$        | Gate to Drain Charge  | 61  | nC | I <sub>D</sub> = 75 A                                | Fig. 12 |

| Qg              | Total Gate Charge     | 211 |    | Per IEC60747-8-4 pg 21                               |         |

12

Poland D'ALITHIED, D&D Ind

axid **IGBT** datasheet IKY50N120CH3 (infineon Fast silicon diode High speed switching series third generation IGBT ajoutée Low switching losses IGBT in Highspeed3 technology copacked with soft, fast recovery full current rated anti-parallel Emitter Controlled diode Rappel : le transistor IGBT ne conduit pas dans le High speed H3 technology offers:

• Ultra-low loss switching losses thanks to Kelvin emitter pin package in combination with High speed H3 technology.

• High efficiency in hard switching and resonant topologies

• 10 uses short circuit withstand time at T<sub>v=</sub>175°C

- Easy paralleling capability due to positive temperature coefficient in V<sub>CE(set)</sub> 3° quadran Coefficient in Ve<sub>Eleaty</sub> capability due to positive temperature coefficient in Ve<sub>Eleaty</sub> Low Gate Charge Q<sub>o</sub>

- Very soft, fast recovery full current anti-parallel diode

- Maximum junction temperature 175°C

- Pb-free lead plating, RoHS compliant

- Complete product spectrum and PSpice Models:

http://www.infineon.com/igbt/ Applications: Industrial UPS Charger

Energy Storage

Three-level Solar String Inverter

### IGBT datasheet – Energie de switching

- 50A (75A pour le SiC) -> presque 2 fois plus d'énergie

- -> 2 fois moins haut en fréquence

#### Switching Characteristic, Inductive Load

| Dt                                                    | Symbol Conditions - |                                                                                  |      | 11   |      |      |

|-------------------------------------------------------|---------------------|----------------------------------------------------------------------------------|------|------|------|------|

| Parameter                                             |                     |                                                                                  | min. | typ. | max. | Unit |

| IGBT Characteristic, at <i>T</i> <sub>vj</sub> = 25°C |                     |                                                                                  |      |      |      |      |

| Turn-on delay time                                    | $t_{\sf d(on)}$     | T <sub>vi</sub> = 25°C,                                                          | -    | 32   | -    | ns   |

| Rise time                                             | t <sub>r</sub>      | $V_{cc} = 600V, I_{c} = 50.0A,$                                                  | -    | 28   | -    | ns   |

| Turn-off delay time                                   | $t_{ m d(off)}$     | $V_{GE} = 0.0/15.0V$ ,<br>$R_{G(on)} = 10.0\Omega$ , $R_{G(off)} = 10.0\Omega$ , | -    | 296  | -    | ns   |

| Fall time                                             | t <sub>f</sub>      | $L\sigma = 90$ nH, $C\sigma = 67$ pF                                             | -    | 29   | -    | ns   |

| Turn-on energy                                        | E <sub>on</sub>     | Lσ, Cσ from Fig. E<br>Energy losses include "tail" and                           | -    | 2.30 | -    | mJ   |

| Turn-off energy                                       | E <sub>off</sub>    | diode reverse recovery.                                                          | -    | 1.90 | -    | mJ   |

| Total switching energy                                | E <sub>ts</sub>     |                                                                                  | -    | 4.20 | -    | mJ   |

XID - Power Electronics Design Office - www.axid-system.com -

15

Roland D'AUTHIER, R&D Inc

15

### SiC vs IGBT

- En 2022 :

- IGBT IKY50N120CH3 -> environ 6€

- SiC C3M0016120K -> environ 50€

- -> l'IGBT a toujours son marché en 2022 !!

7000 1 0001 Elocitorinos Besign Cinico WWW.axia System.com

16

Roland D'AUTHIER, R&D Ing

Exemple dans les onduleurs de véhicule électriques

- AXID – Power Electronics Design Office - www.axid-system.com -

17

Poland D'ALITHIED D&D Inc

17

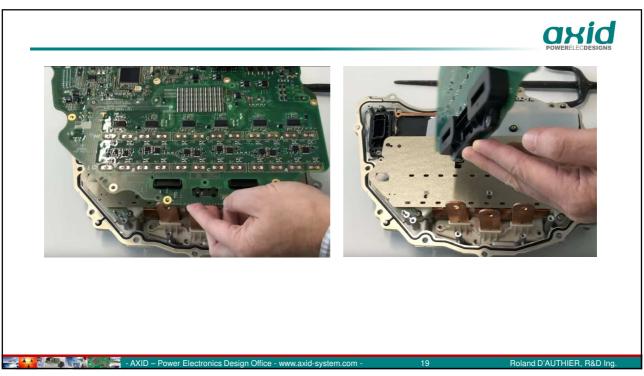

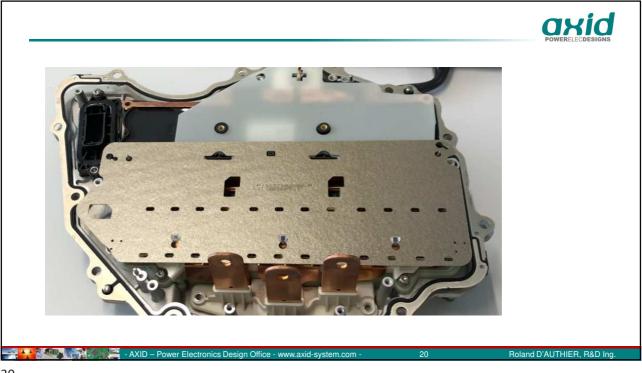

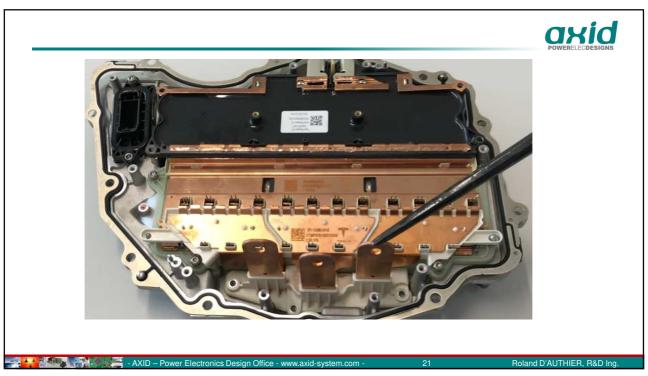

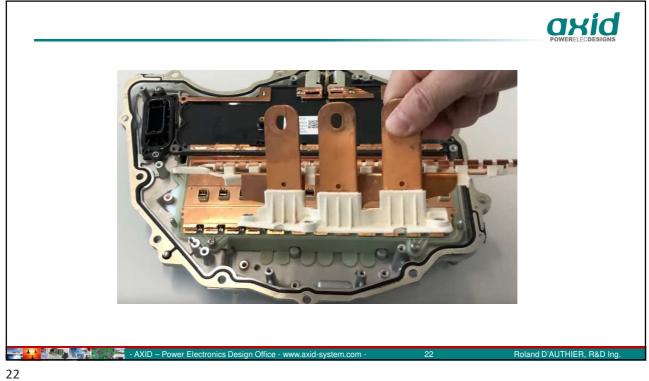

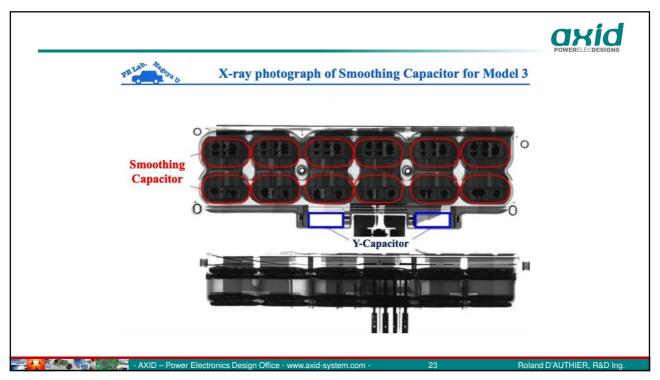

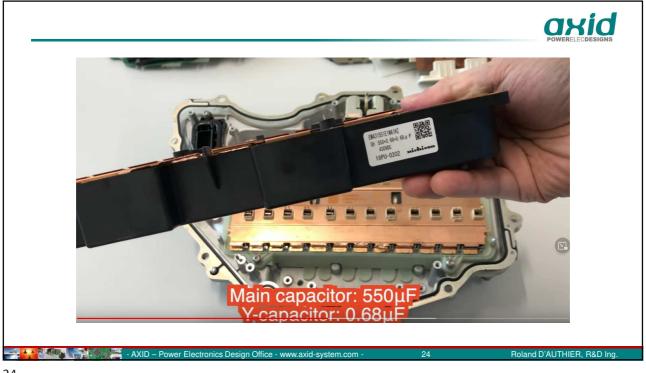

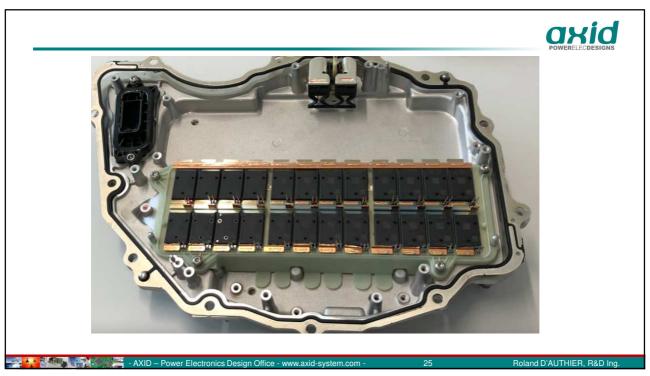

### **TESLA MODEL 3 – Onduleur traction**

https://www.youtube.com/watch?v=fj4KBVgJsGA

AVID Power Flectronics Design Office, www.avid.system.com

18

oland D'AUTHIER, R&D Ing.

### **IGBT vs Jfet SiC**

- Un IGBT à 8kHz a autant de perte de switching que de conduction...

- 2% (IGBT) de perte à comparer à 0,64% (SiC)-> c'est 3 fois mieux

| Voltage<br>Class | Device         | Bus<br>Voltage | Frequency<br>(kHz) | Loss (W)                 |        | Po     | ower Outp | ut     |        |  |

|------------------|----------------|----------------|--------------------|--------------------------|--------|--------|-----------|--------|--------|--|

| Class            |                | voltage        | (KHZ)              |                          | 50 kW  | 100 kW | 150 kW    | 200 kW | 250 kW |  |

|                  |                |                |                    | Conduction               | 341    | 782    | 1322      | 1962   |        |  |

| 750              | IGBT+Diode     | 500            | 8                  | Switching                | 616    | 1064   | 1539      | 2042   |        |  |

| /50              | 750 IGB1+Diode | 300            | 500                | °                        | Total  | 957    | 1846      | 2861   | 4004   |  |

|                  |                |                |                    | Semiconductor Efficiency | 98.09% | 98.15% | 98.09%    | 98.00% |        |  |

|                  |                |                |                    | Conduction               | 62     | 255    | 600       | 1147   | 2016   |  |

| 750              | UJ4SC075006K4S | 500            | 8                  | Switching                | 82     | 102    | 121       | 139    | 157    |  |

| /50              | x 6            | x 6            | 0                  | Total                    | 144    | 357    | 721       | 1286   | 2173   |  |

|                  |                |                |                    | Semiconductor Efficiency | 99.71% | 99.64% | 99.52%    | 99.36% | 99.13% |  |

Table 1: UnitedSiC FETs yield much lower losses than IGBTs in a traction inverter

XID - Power Electronics Design Office - www.axid-system.com -

29

Roland D'AUTHIER, R&D Ind

29

### **MOSFET vs Jfet SiC**

• 2 fois moins de surface à perte égale

| Voltage Class | Devices used         | No of<br>paralleled<br>FETs | Bus Voltage<br>(V) | Freq(kHz) | Total Chip<br>area all<br>phases(mm2) | Total Semi<br>Loss(W) | TJ<br>(Celsius) |

|---------------|----------------------|-----------------------------|--------------------|-----------|---------------------------------------|-----------------------|-----------------|

| 750           |                      | 7                           | 350                | 8         | 462                                   | 3579                  | 159             |

| 750           | G4 SICFET 11m, 750V  | 9                           | 350                | 8         | 594                                   | 2287                  | 122             |

| 750           |                      | 11                          | 350                | 8         | 726                                   | 1753                  | 108             |

| 650           |                      | 7                           | 350                | 8         | 760.2                                 | 2857.5                | 154             |

| 650           | G3 SiCMOS 15m, 650V  | 9                           | 350                | 8         | 977.4                                 | 2129.3                | 125             |

| 650           |                      | 11                          | 350                | 8         | 1194.6                                | 1720.6                | 112             |

| 650           | G2 SiC MOS 20m, 650V | 8                           | 350                | 8         | 1032                                  | 4007.2                | 164             |

| 650           |                      | 10                          | 350                | 8         | 1290                                  | 2825.8                | 130             |

| 650           |                      | 12                          | 350                | 8         | 1548                                  | 2254.7                | 115             |

Table 2: UnitedSiC FETs compared with SiC MOSFETs

- AXID – Power Electronics Design Office - www.axid-system.com

30

Roland D'AUTHIER, R&D Ing.

• Les questions sont les bienvenues

• AXID - Power Electronics Design Office - www.axid-system.com - 32 Roland D'AUTHIER, R&D Ing.

### PARTIE IV – INTEGRATION DANS LES SYSTEMES

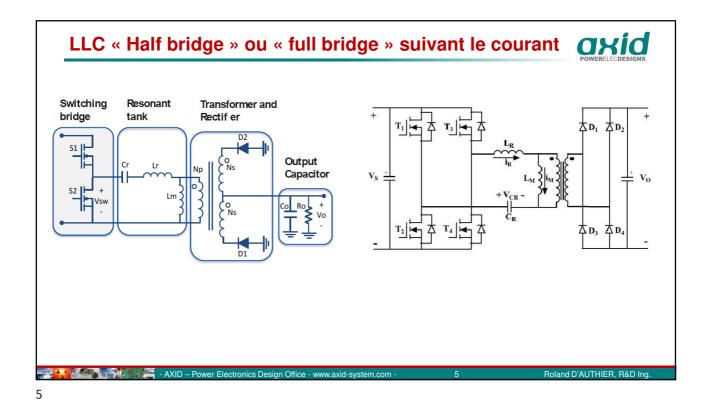

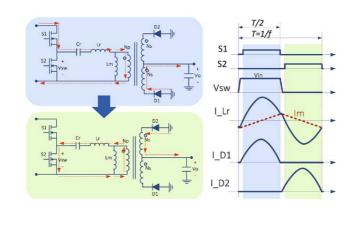

### **LLC - Formation Electronique de Puissance**

Convertisseur isolé « à la mode » multi-résonant à haut rendement

Roland d'Authier - Axid

- AXID – Power Electronics Design Office - www.axid-system.com

Roland D'AUTHIER, R&D Inc

1

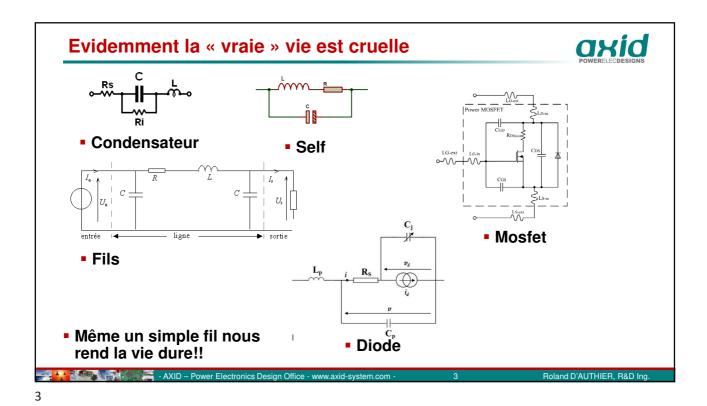

### Les composants électroniques « sans perte »

- Les condensateurs parfaits

- Les selfs parfaites

- Les fils 0 Ohm

- Les circuits ouverts

- Des diodes parfaites

- Des transistors parfaits (bloqué ou fermé)

- Avec ces composants on peut tout imaginer et rester à 100% de rendement!!

- Rappel : 96% de rendement, c'est 2 fois plus de pertes qu'un rendement 98%

- AXID – Power Electronics Design Office - www.axid-system.com -

Roland D'AUTHIER, R&D Ing.

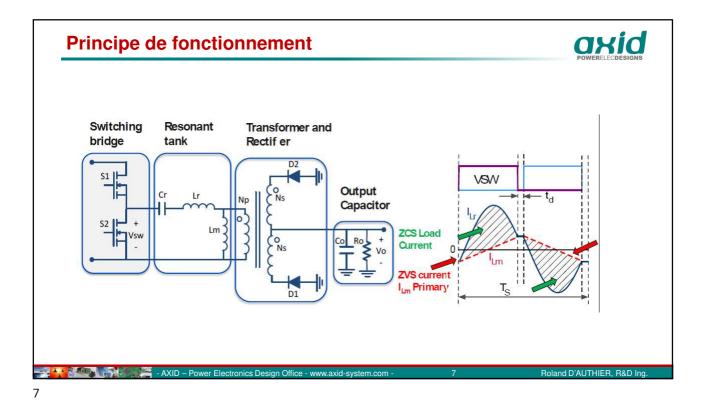

## Le challenge : passer à côté des défauts ou s'en servir

- Dans un convertisseur résonant type LLC on va :

- Utiliser les selfs de fuites des transformateurs et des fils

- Utiliser les condensateurs parasites des transistors

- Annuler (si possible) le courant naturellement avec d'ouvrir un transistor(ZCS)

- Annuler (si possible) la tension naturellement avant de fermer un transistor (ZVS)

- « Démarrer » et « éteindre » doucement les diodes (ZCS)

- ...

- Objectif = passer à côté des pertes de « switching » et monter en fréquence

AVID Power Flectronics Decign Office, MANN avid system com-

Roland D'AUTHIER, R&D Ing.

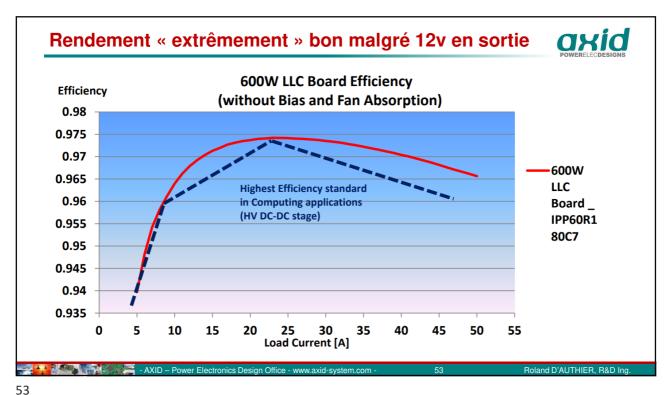

Exemple de design: demoboard Infineon 600W

Ceci est uniquement un exemple

« no endorsement »

EXEMPLE DESIGN:

CECI EST UNIQUEMENT UN EXEMPLE (\* no endorsement )

EXEMPLE DESIGN:

EXEMPLE DESI

(c) Roland D'AUTHIER, AXID, FRAMATECH

### Ce convertisseur se pilote en fréquence

- Ce n'est pas une approche « naturelle »

- Le gain dépend de la charge

- D'habitude pour régler le gain d'un convertisseur on travaille en PWM

- Cette approche nous challenge

- En math

- En physique

- En algorithmie

- En modélisation (fréquentielle + temporelle)

- En contrôle (high resolution timers)

AVID Power Flectronics Design Office, www.avid.system.com

loland D'AUTHIER, R&D Ing.

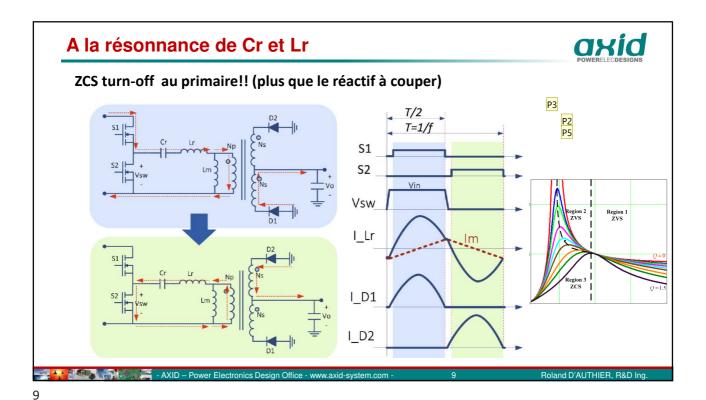

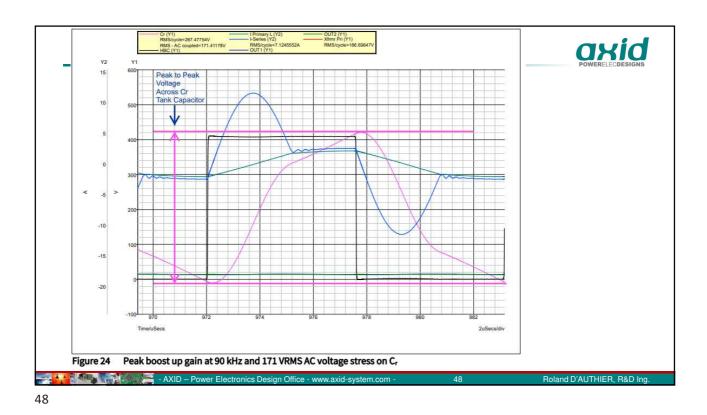

Au dessus de la fréquence de résonance Cr Lr (Région 1) ONE DESIGNES

Pas de ZCS au turn-off au primaire pactif et réactif à couper)

Pas de ZCS au turn-off au secondair

ID 10 Roland DAUTHIER, R&D Ing.

#### **Diapositive 9**

**P2** PCAxid; 01/10/2019

P5 recouvrement de diode est fct du di/dt au moment du passage a 0 et de si la diode est sic ou non, toutefois c'est bien du ZCS PCAxid; 01/10/2019

P3 au secondaire ( diodes)

PCAxid; 01/10/2019

#### **Diapositive 10**

P1 au secondaire ( diiodes)

PCAxid; 01/10/2019

P4 il peut y avoir du ZCS si on est en light laod

PCAxid; 01/10/2019

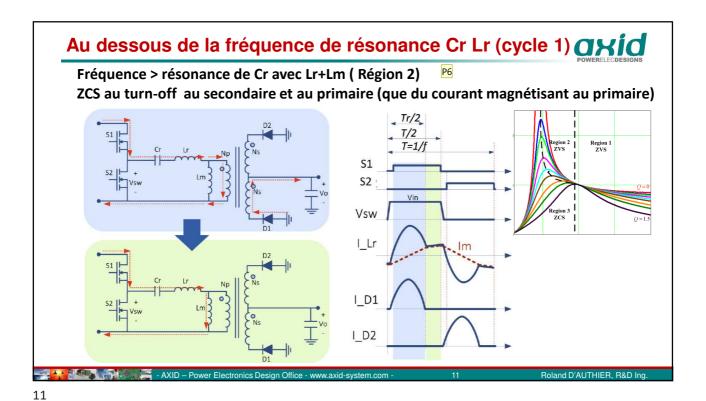

Au dessous de la fréquence de résonance Cr Lr (cycle 2) ONERCLECDESIGNS

TIT/2

### **Diapositive 11**

**P6** graphique avec les 3 zones? pour plus de clareté PCAxid; 01/10/2019

### Région 3 : Zone capacitive interdite

Apparition de hard-switching

la diode-body conduit avant que l'autre transistor se ferme

- -> très forts di/dt au primaire

- -> très forts dv/dt au primaire

Charge de recouvrement inverse Qrr Temps de commutation de la diode

-> casse rapide possible

- AXID – Power Electronics Design Office - www.axid-system.com

13

Roland D'AUTHIER, R&D Ing

13

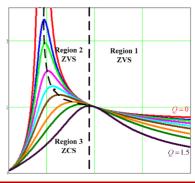

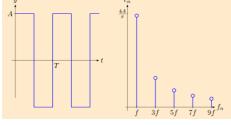

### **FHA = First Harmonic Approximation**

- On a un banc résonant LC

- -> la fréquence joue un rôle important sur le gain

- -> il faut faire des simulations fréquentielles (Bode avec LTerice par exemple)

- Les logiciels de simulation en fréquence et les mathématiciens ont besoin de sinusoïdes et pas de créneaux

- -> on ne va garder que la première harmonique de courant :

$$y(t) = \frac{4A}{\pi} \left[ \sin(2\pi f t) + \frac{1}{3} \sin(2\pi (3f)t) + \frac{1}{5} \sin(2\pi (5f)t) + \frac{1}{7} \sin(2\pi (7f)t) + \dots \right]$$

- AXID – Power Electronics Design Office - www.axid-system.com

14

Roland D'AUTHIER, R&D Ing.

P7 google dit que Niquist: "Le diagramme de Nyquist est un graphe utilisé en électronique et en automatique pour évaluer la stabilité d'un système en boucle fermée. Il représente, dans le plan complexe, la réponse harmonique du système en boucle ouverte correspondante."

PCAxid; 01/10/2019

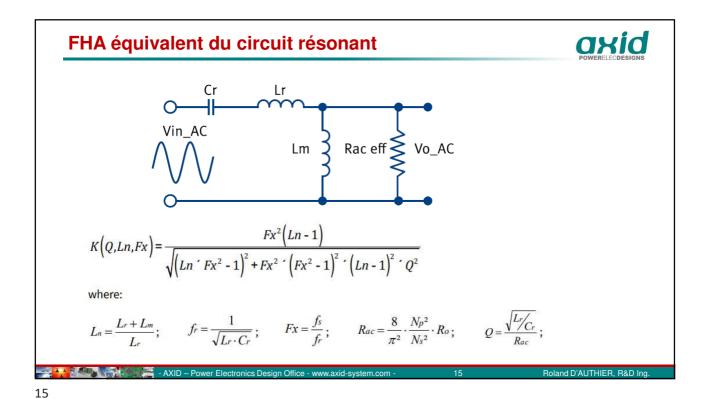

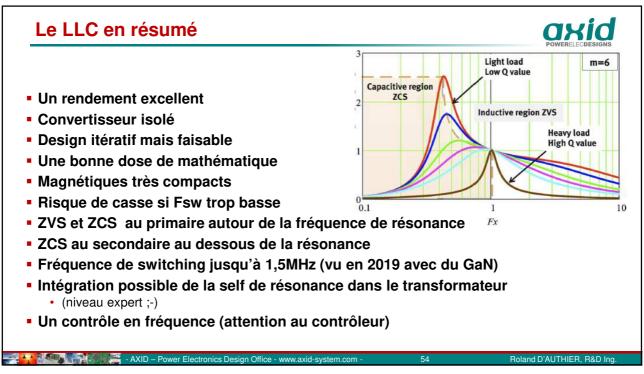

axid Ration Lm/Lr = m = KI = 6Pas très sympa comme courbe de gain ! • En plus il dépend de la charge C'est le prix à payer pour avoir un bon rendement Light load m=6 K(.2, m, Fx)Capacitive region K(.3, m, Fx) $K(.5, m, Fx)^2$ Inductive region ZVS K(.7, m, Fx)Heavy load High Q value K(1, m, Fx)K(5, m, Fx)0.1 Fx 16

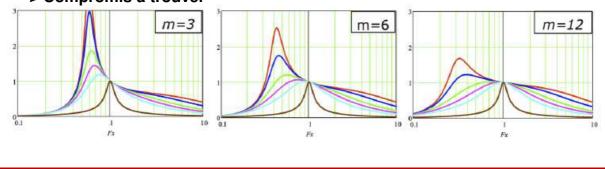

### Comment choisir mon m = Lm/Lr

- Le convertisseur « surtentionne » plus si Lm est proche de Lr

- Par contre si Lm/Lr est petit :

- On a un courant magnétisant important car Lm est petit

- Ce courant ne sert pas au transfert de puissance

- Forte pente en fonction de la fréquence -> attention à la résolution du générateur de fréquence de switching (PulseFreqModulation)

-> Compromis à trouver

7

- AXID - Power Electronics Design Office - www.axid-system.com -

Roland D'AUTHIER, R&D In

17

### **Exemple de design / Cahier des charges**

|  | a | bl | le . | 1 | D | esi) | gn | pa | ara | am | ıe | ter | S |

|--|---|----|------|---|---|------|----|----|-----|----|----|-----|---|

|--|---|----|------|---|---|------|----|----|-----|----|----|-----|---|

| Description                                            | Minimum              | Nominal              | Maximum                                           |

|--------------------------------------------------------|----------------------|----------------------|---------------------------------------------------|

| Input voltage                                          | 350 V <sub>DC</sub>  | 380 V <sub>DC</sub>  | 410 V <sub>DC</sub>                               |

| Output voltage                                         | 11.9 V <sub>DC</sub> | 12.0 V <sub>DC</sub> | 12.1 V <sub>DC</sub>                              |

| Output power                                           |                      |                      | 600 W                                             |

| Efficiency at 50% P <sub>max</sub>                     | 97.5% *              |                      |                                                   |

| Switching frequency                                    | 90 kHz               | 150 kHz              | 250 kHz                                           |

| Dynamic output voltage regulation<br>(0-90% Load step) |                      |                      | Max. overshoot = 0.1 V<br>Max. undershoot = 0.3 V |

| V <sub>out_ripple</sub>                                |                      |                      | 150 mV <sub>pk-pk</sub>                           |

- AXID – Power Electronics Design Office - www.axid-system.com -

Roland D'AUTHIER, R&D Ing.

### Gain du convertisseur

Main transformer turn ratio

$$n = \frac{N_p}{N_s} = \frac{V_{in\_nom}}{2 \cdot V_{out\_nom}} \approx 16$$

Minimum required gain

$$K \min(Q, m, F_x) = \frac{n \cdot V_{o\_min}}{V_{in\_max}/2} \approx 0.95$$

Maximum required gain

$$K \max(Q, m, F_x) = \frac{m \cdot V_{o\_\max}}{V_{in\_\min}/2} \approx 1.08$$

- AXID – Power Electronics Design Office - www.axid-system.com

Roland D'AUTHIER, R&D Ing

19

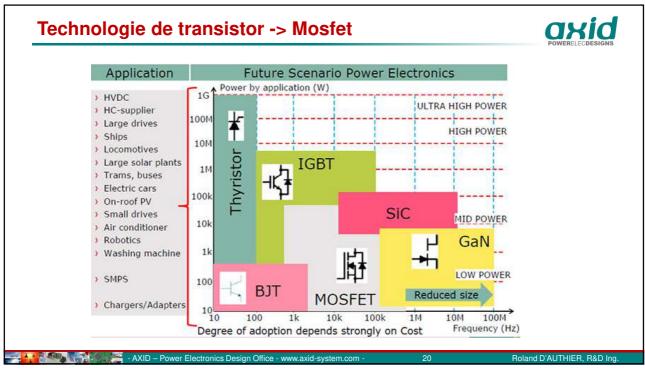

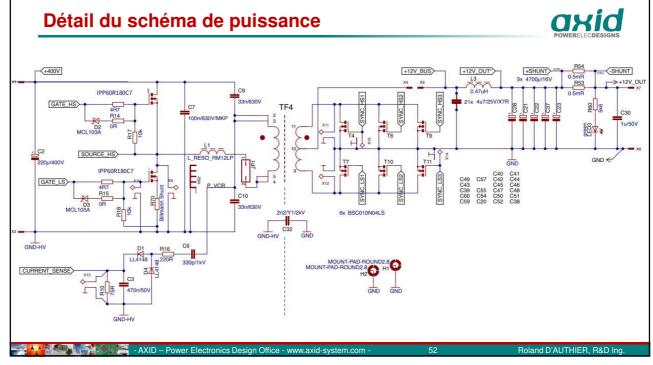

### Choix des transistors au primaire

| Parameter                                  |                     | IPP65R190CFD | IPP60R190P6 | IPP60R180C7 |

|--------------------------------------------|---------------------|--------------|-------------|-------------|

| Effective output capacitance, time related | C <sub>o(tr)</sub>  | 336 pF       | 264 pF      | 349 pF      |

| Gate to drain charge                       | $Q_{gd}$            | 37           | 13 nC       | 8 nC        |

| Internal gate resistance                   | R <sub>g</sub>      | 1.0 Ω        | 3.4 Ω       | 0.85 Ω      |

| Reverse recovery charge                    | Qrr                 | 0.5 μC       | 4 μC        | 2.6 μC      |

| Maximum diode commutation speed            | di <sub>f</sub> /dt | 900 A/μs     | 500 A/μs    | 350 A/μs    |

- AXID – Power Electronics Design Office - www.axid-system.com

Boland D'AUTHIER, R&D Inc

21

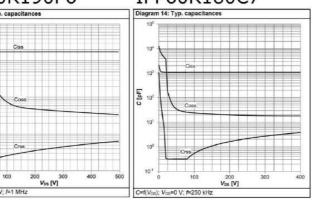

### **ZVS - Coss**, le petit nom d'une des capas parasites

Non seulement on a des parasites mais en plus ils sont non-linéaires

le Coss dépend de la tension aux bornes du transistor

### IPP65R190CFD

#### IPP60R190P6

### IPP60R180C7

- AXID – Power Electronics Design Office - www.axid-system.com -

E 102

Poland D'ALITHIED D&D Inc

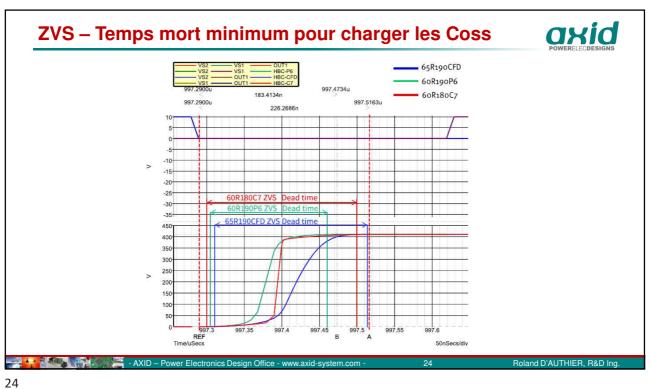

## axid **ZVS - Coss parasite – on s'en sert pour le ZVS** Charge « automatique » pendant le temps mort Il faut que le courant soit en zone inductive Le temps mort doit être assez long pour permettre cette charge avec le courant au moment du swicthing Uin $D_2$

### ZVS – valeur de self magnétisante

- Il faut du courant inductif pour charger les capas Coss

- Ce courant est le courant circulant dans la self magnétisante

- AXID – Power Electronics Design Office - www.axid-system.com

Roland D'AUTHIER, R&D Ing.

25

### **ZVS - Calcul self magnétisante « maximum »**

- + la self magnétisante est petite, plus on a de courant magnétisant

- · Ça facilite le ZVS

- · Ça augmente les pertes

- · moins de ZCS au Turn off primaire

- Plus de pertes de conduction en rdson \* i2

- Le Coss est non linéaire, les constructeurs fournissent des Capacité équivalentes, par exemple Co(tr) pour « Time Related »

- Td typique 100 à 200nS

- Lm max = 180uH

$$L_m = \frac{T_S \times t_d}{16C_{o(tr)}}$$

26

Roland D'AUTHIER, R&D Ing.

### **ZVS – Un bon point pour la CEM**

- La tension du point chaud étant contrôlée par les charges de condensateur Coss

- · -> « pas de violence »

- · Les fronts sont plus doux et moins pentus qu'en hard switching

- · Peu de fuite capacitive entre plan stable et points chaud

- Peu de surtension aux bornes du transistor opposé

- Peu d'oscillation HF

- AXID – Power Electronics Desigr

AXID - Power Electronics Design Office - www.axid-system.com -

27

Poland D'ALITHIED D&D Inc

27

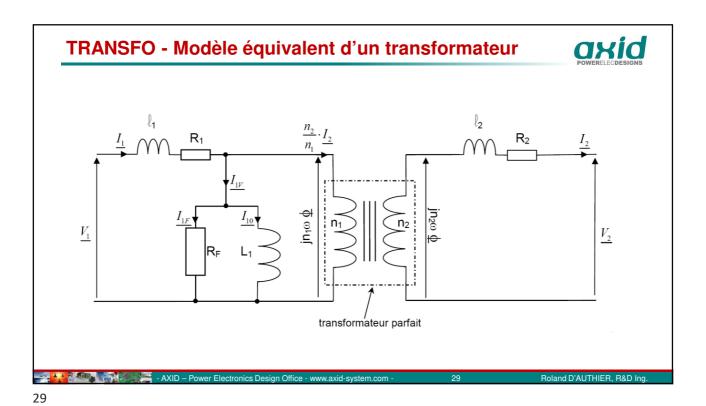

### TRANSFO – Plusieurs technologies de transformateur

- Self de résonance intégrée au transformateur

- Self de résonance externe et transformateur « parfait »

- Bobinage « standard » ou Planar

- PCB ou couches de cuivre ou ruban ou Fils de litz en HF

- Remarque: attention au modèle équivalent utilisé lorsque l'on intègre la self dans le transformateur notamment avec la technologie planar qui réparti la fuite au primaire et au secondaire

- AXID – Power Electronics Design Office - www.axid-system.com

28

Roland D'AUTHIER, R&D Ing.

## TRANSFO – intégration de la self de fuite

- On ajoute un entrefer dans le transformateur

- Ou

- On ajoute un corps magnétique sans secondaire pour profiter du câblage du primaire

## TRANSFO – Design par le bobineur?

- Pas simple d'accéder aux données de certains fabricants de corps magnétiques

- Le design doit être adapté aux capacités techniques du bobineur

- AXID – Power Electronics Design

31

Roland D'AUTHIER, R&D Ind

31

## TRANSFO - Les données d'entrée

- On souhaite un rendement global > 97%

- Le transformateur « perd » en général entre 0,5 et 1% si le design est correct

- Dans l'exemple:

- 0,5% \* 600W = 3W

- Premier critère : il faut trouver un corps magnétique capable de dissiper 3W

- Moins de 110°C avec un ambiant à 55°C:

$$\Delta T_{trafo\_MAX} = \left(110 - 55\right)^{\circ} C = 55^{\circ} C$$

$$Rth_{trafo_{max}} = \frac{\Delta T_{trafo_{Max}}}{P_{trafo_{Max}}} = \frac{55^{\circ}}{3} C / W = 18.3^{\circ} C / W$$

- AXID – Power Electronics Design Office - www.axid-system.com -

32

Roland D'AUTHIER, R&D Ing.

#### TRANSFO - Les données d'entrée

- La fréquence de résonance est fixée à 115kHz (exemple)

- Grâce aux simulations

- · formes de tensions et courant

- au bureau d'étude du bobineur ou si on a le courage on déroule la procédure suivante

- Remarque: la bande de fréquence vérifiée lors des tests CEM démarre souvent à 150kHz...

33

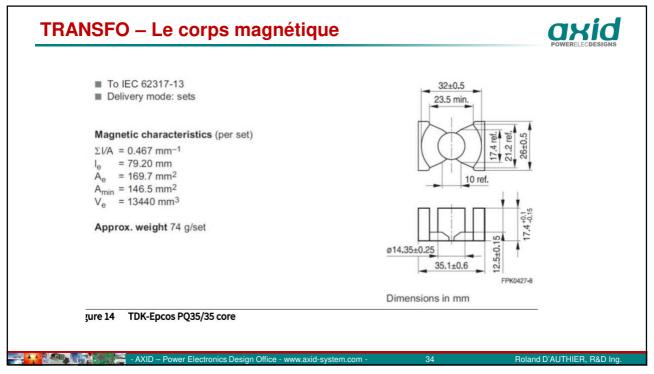

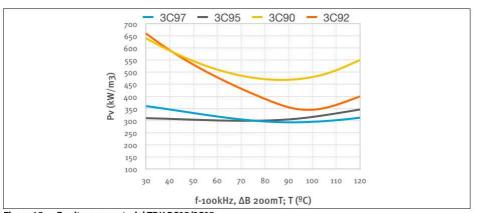

## TRANSFO – Choix du matériau magnétique

■ 3C90 -> pas cher

Figure 15 Ferrite core material TDK PC95/3C95

Delegal DIALITHED, DOD Inc.

35

## TRANSFO – Core PQ3535 (35mm x 35mm)

Core physical parameters Ferroxcube PQ3535 (vendors vary slightly in specified parameters):

$$Ae = 1.9 \cdot 10^{-4}$$

;  $l_m = 0.088$ ;  $Ve = 1.63 \cdot 10^{-5}$ ;  $A_n = 1.52 \cdot 10^{-4}$ ;  $MLT = 0.075$  (10)

- Ae = Aire en m<sup>2</sup> -> 190 mm<sup>2</sup>

- Ve = volume en m3

- MLT = Medium Length Turn en m -> 75 mm

36

Roland D'AUTHIER, R&D Ing.

#### TRANSFO - Calcul du nombre de tours minimum

- La densité de Flux B est

- · Proportionnelle à la tension

- Inversement proportionnelle au nombre de tours

- -> Plus il y a de tours, moins on sature le transfo

- · -> Plus la tension est élevée plus on sature le transfo

- Objectif = limiter la densité de flux

- n'=15= rapport de transfo

$$V_p = n' (V_o + V_f) = 15' (12 + 0.2) = 183V$$

$N_{P_-min} = \frac{n' (V_o + V_f)}{2 \times fmin \times Ae \times DB} = 23.265$

- -> 30 tours au primaire

- -> 2 tours au sesondaire

$$DB = \frac{1}{N_p \times Ae} \times \left(V_o \times n \times \frac{0.5}{fr}\right) = 0.138T$$

AXID - Power Electronics Design Office - www.axid-system.com

37

Roland D'AUTHIER, R&D In

37

## TRANSFO - pertes « fer »

- Dans le corps magnétique ça « bouge » à la fréquence de switching

- Ces fluctuations de champ génèrent des pertes qui dépendent de la fréquence et de la densité de champ

$$P_{core} = a \times \left(\frac{fr}{10^3}\right)^c \times \left(\frac{DB \times 10}{2}\right)^d \times Ve \times \frac{10^{-3}}{10^{-6}} = 0.513W$$

- AXID – Power Electronics Design Office - www.axid-system.com

38

Roland D'AUTHIER, R&D Ing.

#### **TRANSFO – Pertes cuivre**

- Longueur de fil au primaire et au secondaire

- MLT = moyenne d'un tour:

$$l_{wire.pri} = MLT ' N_P = 2.25$$

$$l_{wire.sec} = MLT ' N_S = 0.15$$

Aire de bobinage

$$A_{n_{-}p} = A_n \cdot \frac{k}{2} = 7.6 \cdot 10^{-6}$$

$$A_{n_{-}s} = A_n \cdot \frac{k}{2 \cdot N_{spc}} = 3.8 \cdot 10^{-6}$$

- AXID – Power Electronics Design Office - www.axid-system.com

Roland D'AUTHIER, R&D Ing

39

## TRANSFO - Pertes cuivre

Section du câble

$$A_{wire.pri} = \frac{A_{n_p}}{N_p} = 2.533 \cdot 10^{-7}$$

$$A_{wire.sec} = \frac{A_{n_{-}s}}{N_{s}} = 1.9 \cdot 10^{-6}$$

Résistance des câbles

$$R_{dc\_pri} = \frac{r \times l_{wire.pri}}{A_{wire.pri}} = 0.153$$

$$R_{dc\_sec} = \frac{r \times l_{wire.sec}}{A_{wire.pri}} = 1.361 \times 10^{-3}$$

- AXID – Power Electronics Design Office - www.axid-system.com

40

Roland D'AUTHIER, R&D Ing.

#### TRANSFO - Pertes cuivre

• Pertes en ri<sup>2</sup>

$$Sec_{Loss} = I_{Sec}^{2} R_{dc\_sec} = 3.4W$$

- AXID – Power Electronics Design Office - www.axid-system.com -

41

Roland D'AUTHIER, R&D Inc

41

#### **TRANSFO – Pertes totales**

On arrive à estimer les pertes totales

$$Total_{Loss\_Est} = Pcore + Pri_{Loss} + Sec_{Loss} = 6.617W$$

- Environ 1% dans le transformateur avec un matériau magnétique peu cher

- Ces pertes sont environ divisées par 2 avec un matériau magnétique (3C95) plus performant et une surface de câblage plus grande

AVID Power Flectronics Decign Office, MANN avid system com-

42

Roland D'AUTHIER, R&D Ing

43

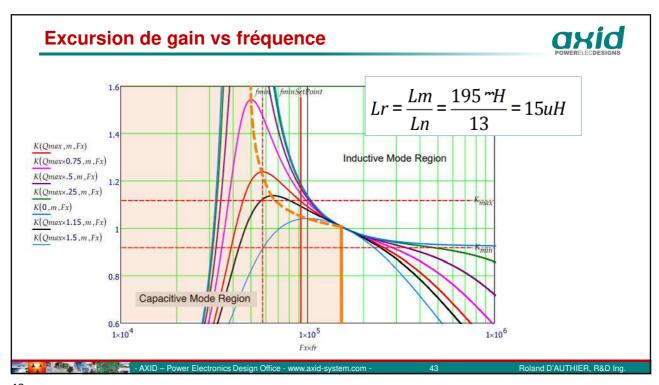

### Le ratio Lm/Lr = KI = m = ...

- Dans cet exemple nous avons une ration de 13

- Peu d'excursion de gain demandée

- On trouve souvent des ratios KI de l'ordre de 5

- · Permet de plus « surtensionner »

$$Lr = \frac{Lm}{Ln} = \frac{195 \, ^nH}{13} = 15uH$$

44

Roland D'AUTHIER, R&D Ing.

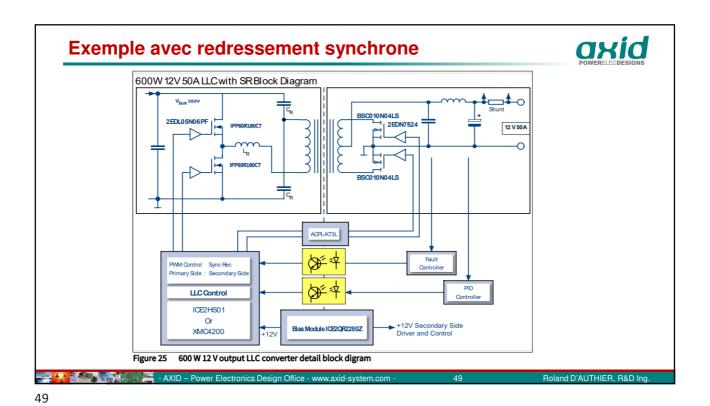

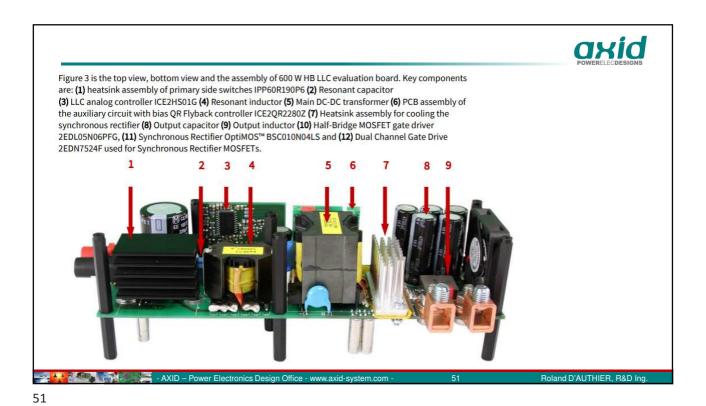

Synchronous rectifier (8) Output capacitor (9) Output inductor (10) Half-Bridge MOSFET gate driver 2EDL05N06PFG, (11) Synchronous Rectifier OptiMOS™ BSC010N04LS and (12) Dual Channel Gate Drive 2EDN7524F used for Synchronous Rectifier MOSFETs.

-

# Une offre de formations adaptée à vos situations professionnelles

#### Contacts

Tél. 04 91 95 55 70 Mail : contact@framatech.fr

Alain BARONI, CEO alain.baroni@framatech.fr

Sheina GUEDJ, Formations sheina.guedj@framatech.fr

FRAMATECH S.A. au capital de 38112 Euros Etudes & mises en œuvre de stratégies industrielles internationales Hautes Technologies

4 boulevard d'Arras - 13004 Marseille - France

Tél. +33 491 95 55 70 / Fax. +33 491 95 55 75 / Mail : contact@framatech.fr

Organisme de formation n° 93060115506 – Siret 344 351 879 00046 – NAF 742C – RC88B126

Web : www.framatech.fr